Nachdem ich die Bibliothek für den LPC3131 bzw. für das Package TFBGA180 erstellt habe, fing ich an, den Schaltplan zu entwerfen. Beim Entwurf habe ich mich nur auf die nötigen Bauteile / Interfaces beschränken.

Nachdem ich die Bibliothek für den LPC3131 bzw. für das Package TFBGA180 erstellt habe, fing ich an, den Schaltplan zu entwerfen. Beim Entwurf habe ich mich nur auf die nötigen Bauteile / Interfaces beschränken.

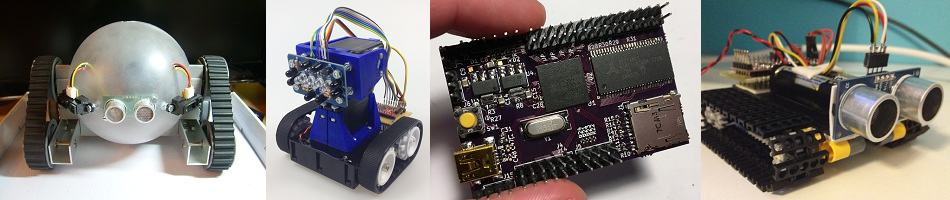

Die Peripherie habe ich auf RAM, Micro SD-Karte, USB und natürlich die Spannungsversorgung beschränkt. Auf LAN habe ich verzichtet und stattdessen das SPI auf einen Pin – Header herausgeführt, was spätere Anbindung ermöglichen würde. Auch weitere Schnittstellen sind über Pin – Header zugänglich, u.A. I2C, UART, einige digitale I/Os (dabei PWM), analoge Inputs, JTAG und die Konfigurationspins, über die man die Boot Quelle auswählen kann.

Auch bei der Spannungsversorgung habe ich etwas gespart. Obwohl ich in letzter Zeit gerne mit Schaltreglern arbeite, habe ich bei dem Prototypen für diese Platine auf „normale“ lineare Spannungsregler (3v3 und 1v2) gesetzt, was im Vergleich zu Schaltreglern etwas günstiger ist.

Der RAM ist mit 256M wohl ein Overkill, kleinere und günstigere RAMs gab es im als BGA Ausführung, aber ich wollte mich bei der Platine auf nur ein BGA beschränken.

Zum Layout gibt es nicht so viel zu sagen. Da es sich auf dem ganzen Board um relativ geringe Taktraten geht, mussten keine Length Matching der Leiterbahnen oder Impedanzkontrolle berücksichtigt werden. Und da es sich hierbei um ein Hobby-Projekt handelt, muss ich hier keine Rücksicht auf irgendwelche Compliances / Signalintegritäten nehmen. Um den ARM Prozessor herum war es für mich auch so schnon kniffelig genug. Ich habe auf dem Gebiet BGA einfach noch nicht genug Erfahrung und mit KiCAD sowieso nicht. Die Kondensatoren und Widerstände sind als 0402 SMD ausgeführt.

Die Platine besteht aus 4 Lagen. Die oberste (rot) und unterste (grün) Lagen beinhalten die Leiterbahnen (Signale und einige für die Versorgung) und die inneren zwei sind Ground und 3,3 Volt. Diese inneren zwei Lagen erleichtern einem das Leben. Beim Routen unter dem BGA führt man nur die Leiterbahn vom Pad evtl. auf ein Kondensator und dann auf ein Via und … Punkt. Die Vias verbinden sich in den inneren Layern automatisch mit Ground oder 3V3.

Die Platine besteht aus 4 Lagen. Die oberste (rot) und unterste (grün) Lagen beinhalten die Leiterbahnen (Signale und einige für die Versorgung) und die inneren zwei sind Ground und 3,3 Volt. Diese inneren zwei Lagen erleichtern einem das Leben. Beim Routen unter dem BGA führt man nur die Leiterbahn vom Pad evtl. auf ein Kondensator und dann auf ein Via und … Punkt. Die Vias verbinden sich in den inneren Layern automatisch mit Ground oder 3V3.

In dem nachfolgenden Bild wird es hoffentlich etwas deutlicher.

Die roten Leiterbahnen befinden sich auf der obersten Lage. Eine Lage runter befindet sich die 3,3V Plane (gelb) und noch eine Lage Runter befindet sich die GND Plane (pink).

Die roten Leiterbahnen befinden sich auf der obersten Lage. Eine Lage runter befindet sich die 3,3V Plane (gelb) und noch eine Lage Runter befindet sich die GND Plane (pink).